AT89C51RD2/ED2:8位闪存微控制器

发布日期:2025-08-25

特性

•兼容80C52

–8051指令兼容

–六个8位I/O端口(64引脚或68引脚版本)

–四个8位I/O端口(44引脚版本)

–三个16位定时器/计数器

–256字节擦写板RAM

–9个中断源,4个优先级

•集成电源监控器(POR/PFD),用于监控内部电源

•使用标准VCC电源的ISP(系统内编程)

•2048字节引导ROM包含低级闪存编程例程和默认串行加载器

•高速架构

–在标准模式下:

•40 MHz(Vcc 2.7V至5.5V,内部和外部代码执行)

•60 MHz(Vcc 4.5V至5.5V,仅限内部代码执行)

–在X2模式下(6个时钟/机器周期)

•20 MHz(Vcc 2.7V至5.5V,内部和外部代码执行)

•30 MHz(Vcc 4.5V至5.5V,仅限内部代码执行)

•64K字节片上闪存程序/数据存储器

-字节和页(128字节)擦除和写入

–100k写入周期

•片上1792字节扩展RAM(XRAM)

–软件可选大小(0、256、512、768、1024、1792字节)

–重置时选择768字节以兼容T89C51RD2

•用于数据存储的片上2048字节EEPROM块(仅限AT89C51ED2)

•100K写入周期

•双数据指针

•适用于慢速RAM/外围设备的可变长度MOVX

•改进了X2模式,CPU和每个外围设备都可以独立选择

•端口1上的键盘中断接口

•SPI接口(主/从模式)

•8位时钟预分频器

•16位可编程计数器阵列

–高速输出

–比较/捕捉

–脉宽调制器

–看门狗定时器功能

•异步端口重置

•全双工增强型UART,带专用内部波特率发生器

•低电磁干扰(抑制ALE)

•硬件看门狗定时器(一次性启用并重置),电源关闭标志

•电源控制模式:空闲模式、断电模式

•单量程电源:2.7V至5.5V

•工业温度范围(-40至+85°C)

•封装:PLCC44、VQFP44、PLCC68、VQFP64

描述

AT89C51RD2/ED2是80C51 CMOS单芯片8位微控制器的高性能CMOS闪存版本。它包含一个用于代码和数据的64KB闪存块。

64KB闪存可以通过ISP功能或软件以并行模式或串行模式进行编程。编程电压由标准VCC引脚内部产生。

AT89C51RD2/ED2保留了Atmel 80C52的所有功能,具有256字节的内部RAM、9源4级中断控制器和三个定时器/计数器。AT89C51ED2提供2048字节的EEPROM用于非易失性数据存储。

此外,AT89C51RD2/ED2具有可编程计数器阵列、1792字节的XRAM、硬件看门狗定时器、SPI接口、键盘、促进多处理器通信的多功能串行通道(EUART)和速度改进机制(X2模式)。

AT89C51RD2/ED2的全静态设计允许通过将时钟频率降至任何值(包括直流)来降低系统功耗,而不会丢失数据。

AT89C51RD2/ED2具有2种软件可选的减少活动模式和8位时钟预分频器,可进一步降低功耗。在空闲模式下,CPU被冻结,而外围设备和中断系统仍在运行。在断电模式下,RAM被保存,所有其他功能均不工作。

AT89C51RD2/ED2的附加功能使其在需要脉宽调制、高速I/O和计数功能的应用中更加强大,如报警、电机控制、有线电话和智能卡读卡器。

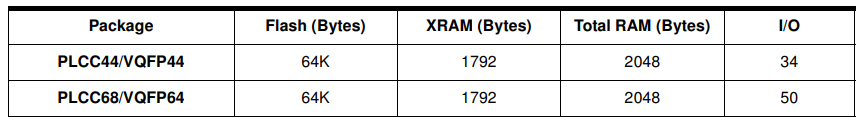

表1.内存大小和I/O引脚

端口类型

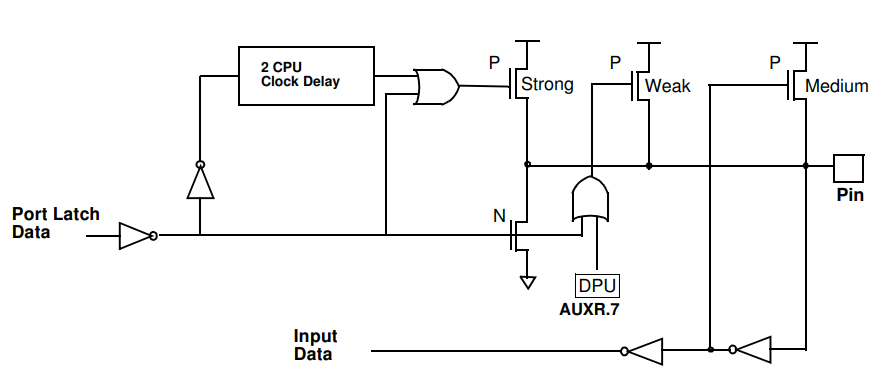

AT89C51RD2/ED2 I/O端口(P1、P2、P3、P4、P5)实现了80C51及其大多数衍生产品上常见的准双向输出。这种输出类型可以同时用作输入和输出,而无需重新配置端口。这是可能的,因为当端口输出逻辑高时,它被弱驱动,允许外部设备将引脚拉低。当引脚被拉低时,它被强烈驱动,能够吸收相当大的电流。这些特性与开漏输出有些相似,除了准双向输出中有三个上拉晶体管用于不同的目的。其中一种上拉,称为“弱”上拉,只要引脚的端口锁存器包含逻辑1,就会打开。弱拉将产生一个非常小的电流,如果引脚保持浮动状态,该电流将把引脚拉高。当引脚的端口锁存器包含逻辑1并且引脚本身也处于逻辑1电平时,会打开第二个上拉,称为“中等”上拉。该上拉为输出1的准双向引脚提供主源电流。如果外部设备将其上具有逻辑1的引脚拉低,则介质上拉关闭,只有弱上拉保持打开。为了在这些条件下将引脚拉低电压,外部设备必须吸收足够的电流来压倒介质上拉,并使端口引脚上的电压低于其输入阈值。

第三种上拉被称为“强”上拉。当端口锁存器从逻辑0变为逻辑1时,这种上拉用于加速准双向端口引脚上的低到高转换。当这种情况发生时,强上拉会短暂开启,两个CPU时钟,以便快速将端口引脚拉高。然后它再次关闭。

DPU位(AUXR寄存器中的位7)允许在锁存数据为逻辑0时禁用所有端口的永久弱上拉。准双向端口配置如图1所示。

图1:准双向输出

振荡器

为了优化特定任务所需的功耗和执行时间,在振荡器和CPU及外围设备之间实现了内部分频器功能。

增强功能

与原来的80C52相比,AT89C51RD2/ED2实现了一些新功能,包括:

•X2选项

•双数据指针

•扩展RAM

•可编程计数器阵列(PCA)

•硬件监视器

•SPI接口

•4级中断优先级系统

•电源关闭标志

•一次模式

•ALE禁用

•UART和定时器2中也有一些增强功能

X2功能

AT89C51RD2/ED2内核每个机器周期只需要6个时钟周期。这个名为“X2”的功能具有以下优点:

•将频率晶体除以2(更便宜的晶体),同时保持相同的CPU功耗。

•在保持CPU功率不变的同时节省功耗(振荡器节能)。

•在运行和空闲模式下,通过将工作频率动态除以2来节省功耗。

•在保持晶体频率不变的情况下,将CPU功率增加2。

为了保持原始的C51兼容性,在XTAL1信号和核心(相位发生器)的主时钟输入之间插入了一个2的除法器。此分隔器可能会被软件禁用。

描述

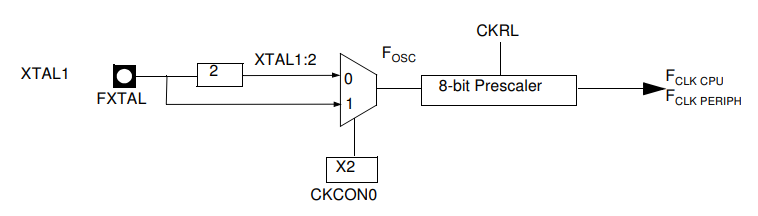

整个电路和外围设备的时钟首先被除以2,然后由CPU内核和外围设备使用。

这允许在XTAL1输入上接受任何循环比率。在X2模式下,由于该分频器被旁路,XTAL1上的信号必须具有40%至60%的循环比。

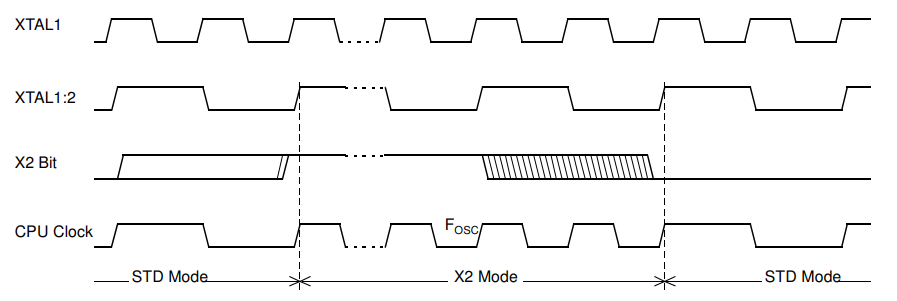

图2显示了时钟生成框图。X2位在XTAL1÷2的上升沿进行验证,以避免从X2切换到STD模式时出现故障。图3显示了切换模式波形。

图2:时钟生成图

图3:模式切换波形

CKCON0寄存器中的X2位允许从12个时钟周期指令切换到6个时钟周期,反之亦然。重置时,速度根据硬件安全字节(HSB)的X2位设置。默认情况下,标准模式处于活动状态。设置X2位可激活X2功能(X2模式)。

CKCON0寄存器中的T0X2、T1X2、T2X2、UartX2、PcaX2和WdX2位以及CKCON1寄存器中的SPIX2位允许从标准外设速度(每个外设时钟周期12个时钟周期)切换到快速外设速度(每个外设时钟周期6个时钟时段)。这些位仅在X2模式下有效。

双数据指针寄存器(DPTR)

附加的数据指针可用于加速代码执行并减小代码大小。

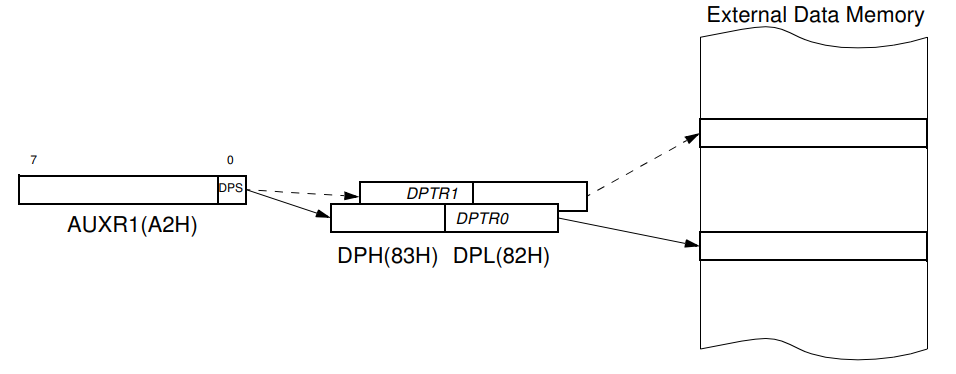

双DPTR结构是芯片指定外部数据存储器位置地址的一种方式。有两个16位DPTR寄存器用于寻址外部存储器,还有一个名为DPS=AUXR1.0的位,允许程序代码在它们之间切换(见图4)。

图4:双指针的使用

INC是一种短(2个字节)和快速(12个时钟)的方式来操纵AUXR1 SFR中的DPS位。但是,请注意,INC指令不会直接将DPS位强制到特定状态,而只是将其切换。在简单的例程中,例如块移动示例,只有DPSs以正确的顺序切换的事实才重要,而不是它的实际值。换句话说,无论DPS在输入时是“0”还是“1”,块移动例程的工作原理都是一样的。观察到,如果没有最后一条指令(INC AUXR1),例程将退出,DPS处于相反状态。

扩展RAM(XRAM)

AT89C51RD2/ED2提供了额外的片上随机存取存储器(RAM)空间,用于增加数据参数处理和高级语言使用。AT89C51RD2/ED2设备在外部数据空间中具有扩展RAM,可配置高达1792字节。

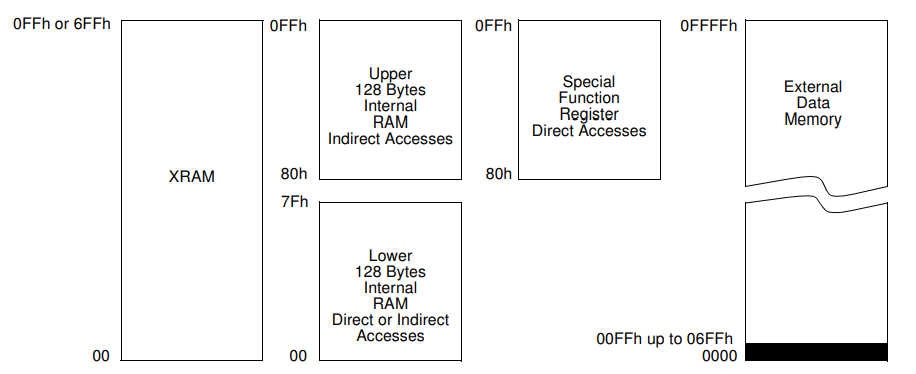

AT89C51RD2/ED2内部数据存储器被映射到四个单独的段。这四个部分是:

1.RAM的低128字节(地址00h至7Fh)可以直接和间接寻址。

2.RAM的上128字节(地址80h至FFh)只能间接寻址。

3.特殊功能寄存器SFR(地址80h至FFh)只能直接寻址。

4.扩展RAM字节由MOVX指令间接访问,并在AUXR寄存器中清除EXTRAM位。

较低的128个字节可以通过直接或间接寻址来访问。只能通过间接寻址访问128个字节。高位128字节与SFR占用相同的地址空间。这意味着它们具有相同的地址,但在物理上与SFR空间分开。

图5:内部和外部数据存储器地址

当指令访问地址7Fh以上的内部位置时,CPU知道该访问是通过指令中使用的寻址模式访问数据RAM的上128字节还是SFR空间。

•使用直接寻址访问SFR空间的指令。例如:MOV 0A0H,#data,访问位置0A0H(即P2)处的SFR。

•使用间接寻址的指令访问数据RAM的上128字节。例如:MOV@R0,#data,其中R0包含0A0h,访问地址0A0h处的数据字节,而不是P2(其地址为0A0h)。

•XRAM字节可以通过间接寻址进行访问,清除EXTRAM位和MOVX指令。这部分存储器物理上位于片上,逻辑上占据外部数据存储器的第一个字节。如表9-1所示,比特XRS0和XRS1用于隐藏可用XRAM的一部分。如果外部外围设备映射到内部XRAM已经使用的地址,这可能很有用。

•当EXTRAM=0时,使用MOVX指令与所选存储体或DPTR的寄存器R0、R1中的任何一个结合,间接寻址XRAM。对XRAM的访问不会影响端口P0、P2、P3.6(WR)和P3.7(RD)。例如,当EXTRAM=0时,MOVX@R0,#数据,其中R0包含0A0H,访问地址0A0Hrather处的XRAM,而不是外部存储器。将使用MOVX DPTR指令以与标准80C51中相同的方式对高于XRAM可访问大小的外部数据存储器位置进行访问,P0和P2作为数据/地址总线,P3.6和P3.7作为写和读定时信号。只有使用DPTR才能访问0FFH以上的XRAM。

•当EXTRAM=1时,MOVX@Ri和MOVX@DPTR将类似于标准80C51。MOVX@Ri将提供与Port0上的数据复用的8位地址,任何输出端口引脚都可以用于输出更高阶的地址位。这是为了提供外部寻呼功能。MOVX@DPTR将生成一个16位地址。Port2输出高位八个地址位(DPH的内容),而Port0将低位八个地址位数(DPL)与数据复用。MOVX@Ri和MOVX@DPTR将在P3.6(WR)和P3.7(RD)上产生读或写信号。

堆栈指针(SP)可以位于256字节RAM(下RAM和上RAM)内部数据存储器中的任何位置。堆栈可能不在XRAM中。M0位允许扩展XRAM定时;如果设置了M0,则读和写脉冲从6个时钟周期延长到30个时钟周期。这对于访问外部慢速外围设备非常有用。